# Circuitos Lógicos

#### Profa. Grace S. Deaecto

Faculdade de Engenharia Mecânica / UNICAMP 13083-860, Campinas, SP, Brasil. grace@fem.unicamp.br

Segundo Semestre de 2013

#### NOTA AO LEITOR

Estas notas de aula foram inteiramente baseadas nas seguintes referências :

- T. Floyd, "Digital Fundamentals", 10th Edition, Prentice Hall, 2009.

- R. J. Tocci, N. S. Widmer, G. L. Moss, "Sistemas Digitais: Princípios e Aplicações", Prentice-Hall, 2007.

- S. Brown, Z. Vranesic, "Fundamentals of Digital Logic with Verilog Design", McGrawHill, 2003.

- I. V. Iodeta, F. G. Capuano, "Elementos de Eletrônica Digital", Editora Érica, 2006.

- V. A. Pedroni, "Circuit Design and Simulation with VHDL", 2<sup>nd</sup> Edition, MIT, 2010.

- Memórias

- Memória ROM

- Memória RAM

3 / 23

#### Memórias

- O foco deste capítulo é o estudo das memórias, que são dispositivos com alta capacidade de armazenamento de informação.

- Basicamente, a memória é uma parte do computador responsável pelo armazenamento de dados binários.

Normalmente, é acessada milhões de vezes por segundo e, por esta razão, tempo de acesso e precisão são características essenciais que as qualificam.

- A seguir, apresentaremos algumas definições importantes.

#### Estrutura da memória

- A memória armazena informações em forma de matrizes de dados.

- Cada elemento desta matriz, conhecido como célula, corresponde a um bit.

- De maneira geral, as memórias são especificadas pela sua capacidade de armazenamento, ou seja, pelo produto n × m, sendo n o número de palavras que ela pode armazenar e m o tamanho de cada palavra.

- Uma memória de 64 células (bits) de capacidade, por exemplo, pode ser organizada de várias maneiras diferentes  $8\times 8$ ,  $16\times 4$ ,  $64\times 1$ .

5 / 23

#### Estrutura da memória

- Algumas memórias usuais são  $32 \times 8$ ,  $128 \times 8$ ,  $1k \times 4$ ,  $64k \times 8$ ,  $2M \times 16$ .

- Note que o número de palavras é sempre uma potência de 2, logo

$$1k = 2^{10} = 1024$$

$1M = 2^{20} = 1048576$

$1G = 2^{30} = 1073741824$

- Por exemplo, a memória  $2M \times 16$  tem capacidade de armazenar 2 147 483 648 palavras de 16 bits cada.

- Cada palavra está localizada em um endereço da memória. No exemplo  $2M \times 16$  o endereço deve ter 21 bits.

6 / 23

Profa. Grace S. Deaecto ES572 DMC / FEM - Unicamp

#### Estrutura da memória

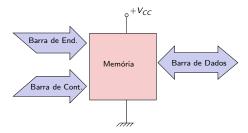

A figura a seguir apresenta um esquema de organização da memória.

- O endereço chega à memória através do barramento de endereços.

- As entradas e saídas de dados são realizadas através do barramento de dados que é bidirecional de forma a permitir escrita e leitura.

- Além disso, as opções de escrita e leitura são definidas através do barramento de controle.

Profa. Grace S. Deaecto ES572 DMC / FEM - Unicamp 7 / 23

## Classificação das memórias

Os principais itens usados na classificação das memórias estão listados a seguir :

- Tempo de acesso : É o tempo necessário desde a entrada de um endereço no barramento até o momento em que a informação é disponibilizada na saída.

- O acesso à memória pode ser de duas maneiras distintas :

- Acesso sequencial: Em que para acessar um certo endereço, deve-se percorrer todos os endereços intermediários. Exemplo: fitas magnéticas.

- Acesso aleatório : Permite acessar um endereço diretamente, sem passar pelos endereços intermediários. Exemplo : memória RAM.

## Classificação das memórias

- Volatilidade: Memórias voláteis são aquelas que perdem as informações armazenadas quando a fonte de alimentação é cortada. Exemplo: memória RAM. As não voláteis não perdem as informações quando é cessada a alimentação. Exemplo: memória ROM, PROM, EPROM.

- Troca de dados: As memórias podem ser de escrita e de leitura (memória RAM) ou apenas de escrita (memória ROM).

- Tipo de armazenamento : Quanto ao tipo de armazenamento, elas podem ser estáticas ou dinâmicas.

- Memórias estáticas: Normalmente, utilizam latches para o armazenamento de dados. Nestas memórias, uma vez que o dado é inserido, ele lá permanece. São mais rápidas do que as dinâmicas.

- Memórias dinâmicas: Utilizam capacitores para o armazenamento de dados. Desta forma, para que não haja perda, a informação precisa ser reinserida de tempos em tempos em um processo conhecido como "refreshing". Por serem de arquitetura mais simples, possuem maior capacidade de armazenamento do que as estáticas.

- As memórias ROM (Read Only Memory) têm como característica principal permitir somente a leitura de dados previamente gravados durante sua fabricação.

- Possuem acesso aleatório aos dados e não são voláteis.

- Normalmente, s\u00e3o utilizadas para o armazenamento de programas de sistemas operacionais.

- No seu barramento de controle o CS (chip select), quando em nível baixo, habilita as saídas para fornecimento dos dados.

Quando em nível alto, fica no estado de alta impedância (tri-state) liberando o barramento de dados para outros dispositivos.

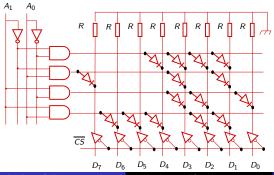

• A figura a seguir apresenta a arquitetura interna de uma memória ROM  $4 \times 8$  com o seguinte conteúdo de dados.

| Endereços |       | Dados |       |       |       |       |       |       |       |       |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| $A_1$     | $A_0$ | Hex   | $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |  |

| 0         | 0     | 1E    | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 0     |  |

| 0         | 1     | 8A    | 1     | 0     | 0     | 0     | 1     | 0     | 1     | 0     |  |

| 1         | 0     | 0D    | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 1     |  |

| 1         | 1     | 76    | 0     | 1     | 1     | 1     | 0     | 1     | 1     | 0     |  |

| Γ | Н | Chave    | Ε | S          |

|---|---|----------|---|------------|

| Γ | 0 | fechada  | 0 | 0          |

|   | U | recriada | 1 | 1          |

| Γ | 1 | aberta   | Х | alta       |

| L |   |          |   | impedância |

Profa. Grace S. Deaecto

ES572

DMC / FEM - Unicamp

12 / 23

- Na figura anterior o decodificador de endereços pode ser facilmente identificado.

- Considerando que o CS está em nível baixo, quando um endereço é selecionado, apenas um dos fios é ativado pelo decodificador de endereços. Desta forma, as quedas de tensão nos resistores devido à presença dos diodos em posições adequadas fornecem os dados na saída.

- Dependendo da tecnologia de fabricação as matrizes de dados podem ser projetadas com transistores bipolares ou com transistores de efeito de campo MOSFET.

- Normalmente o fabricante utiliza um gabarito fotográfico das ligações elétricas chamado de máscara, sendo as memórias assim confeccionadas denominadas ROM programadas por máscara.

- Memórias PROM (Programmable Read-Only Memory) Podem ser programadas pelo usuário, mas de maneira definitiva. O princípio básico de programação consiste em destruir, através de nível de tensão especificado pelo fabricante, pequenas ligações semicondutoras existentes.

- Memórias EPROM (Erasable Programmable Read-Only Memory) -São memórias ROM programáveis e apagáveis. Podem ser programadas pelo usuário sendo a programação realizada de maneira semelhante a da memória PROM. A vantagem é que podem ser apagadas por irradiação de luz ultravioleta na pastilha por uma janela existente em seu encapsulamento. Também conhecidas como UVPROM.

- Memórias EEPROM (Electrically Erasable Programmable Read-Only Memory) - Permitem que o apagamento de dados seja feito eletricamente e isoladamente por palavras de dados. Não é necessário desconectar a memória do circuito integrado durante as alterações de programação. São memórias de escrita e leitura e como todas acima, não voláteis e de acesso aleatório.

- As memórias RAM (Random Access Memory) são de acesso aleatório, voláteis e possuem um tempo de acesso bastante reduzido.

- Normalmente são utilizadas como memórias de programas e dados para armazenamento temporário.

- Quanto ao armazenamento podem ser estáticas (SRAM) ou dinâmicas (DRAM).

- No seu barramento de controle além do  $\overline{CS}$  (chip select) existe o terminal  $R/\overline{W}$  (Read/Write) de dupla função que permite a leitura  $R/\overline{W}=1$  ou a escrita  $R/\overline{W}=0$  dos dados nas localidades endereçadas.

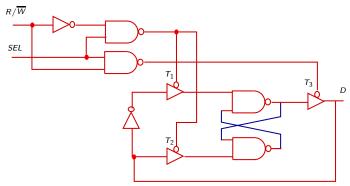

Para entendermos o seu funcionamento, vamos analisar o circuito de uma célula básica que permite escrita e leitura.

- O sinal de controle SEL = 1 habilita a memória para a operação de escrita ou leitura de dados. Quando SEL = 0 as duas portas NAND apresentam nível alto na saída fazendo os tri-states funcionarem como chaves abertas.

- Operação de escrita : Aplica-se SEL=1 e  $R/\overline{W}=0$  nos sinais de controle. Desta forma, os tri-states  $T_1$  e  $T_2$  operam como chaves fechadas e  $T_3$  como chave aberta. O dado é aplicado em D e armazenado no latch.

- Operação de leitura : Aplica-se SEL=1 e  $R/\overline{W}=1$  nos sinais de controle. Desta forma, os tri-states  $T_1$  e  $T_2$  operam como chaves abertas e  $T_3$  como chave fechada. O dado que estava armazenado no latch fica disponível em D.

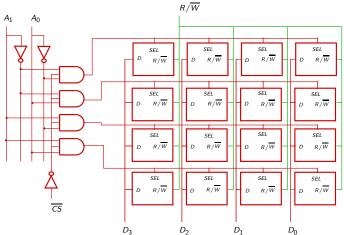

• Utilizando a célula anterior, a figura a seguir apresenta a arquitetura interna de uma memória RAM  $4 \times 4$ .

18 / 23

A operação no modo escrita ou leitura ocorre da seguinte maneira :

- Primeiramente habilita-se o barramento de dados fazendo  $\overline{CS} = 0$ .

- O decodificador seleciona apenas uma linha de dados fazendo SEL=1 na linha selecionada e nas demais SEL=0.

- Se  $R/\overline{W}=0$  a operação escrita é selecionada sendo que os dados aplicados em  $D_3$   $D_2$   $D_1$   $D_0$  são armazenados na memória. Caso contrário, a operação leitura é seleciona fazendo com que os dados previamente armazenados na memória sejam disponibilizados na saída.

- Vale ressaltar que a informação é perdida caso se desligue a fonte de alimentação.

- A expansão pode ser feita para o tamanho da palavra de dados, para quantidade de endereços ou para ambos.

- Expansão do tamanho da palavra Vamos supor que desejamos obter uma memória RAM de 256 × 8 a partir de dois blocos de estrutura 256 × 4. Para isto basta interligar os barramentos de endereço (A<sub>0</sub> ··· A<sub>7</sub>) e os de controle, ou seja, CS e R/W. O barramento de dados será composto pela associação do barramento de ambos os blocos e passa a ter, portanto, 8 bits como desejado.

• Expansão do tamanho da palavra.

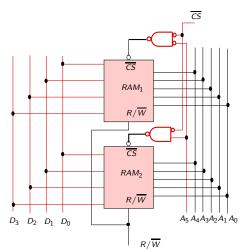

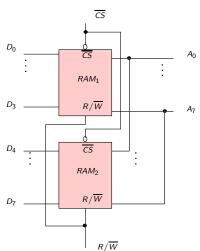

Expansão da quantidade de endereços - Vamos supor que desejamos obter uma memória RAM de 64 × 4 utilizando blocos de estrutura 32 × 4. Para realizar o endereçamento é necessário utilizar uma linha de endereço adicional uma vez que necessitamos de 6 bits para endereçar 64 palavras e cada bloco possui 5 bits para endereçamento de 32 palavras. O esquema está apresentado a seguir.

Profa. Grace S. Deaecto

ES572

DMC / FEM - Unicamp

22 / 23

• Expansão da quantidade de endereços.